# EFFICIENCY AND APPLICATIONS OF SAT-BASED TEST PATTERN GENERATION

- COMPLEX FAULT MODELS AND OPTIMISATION PROBLEMS -

Dissertation zur Erlangung des Doktorgrades (Dr. rer. nat.) der Technischen Fakultät der Albert-Ludwigs-Universität in Freiburg im Breisgau

vorgelegt von

## ALEXANDER CZUTRO, GEB. YÁNEZ-TRUJILLO

im Juni 2013

Dekan der Fakultät:

Prof. Dr. Yiannos Manoli

GUTACHTER:

**Prof. Dr. Bernd Becker** Albert-Ludwigs-Universität Freiburg Freiburg im Breisgau

**Prof. Sudhakar M. Reddy** University of Iowa Iowa City, IA, USA

DATUM DER PROMOTION:

12. August 2013

### **ACKNOWLEDGEMENTS**

First of all, thanks to the adviser of this thesis, Prof. Dr. Bernd Becker, for all the support, help and encouragement I have received from him over the course of many years, and also for having introduced me to the world of scientific research at a very early stage of my undergraduate studies, which has significantly shaped my life in a positive way. And in particular, for giving me the opportunity to present my work at numerous symposia and workshops, thus allowing me to obtain valuable feedback from a large, international community of researchers.

Very special thanks to Prof. Sudhakar M. Reddy (University of Iowa) for the helpful tips that he provided in multiple occasions, and in general, for his ever-present willingness to share his vast knowledge.

My work would not have been possible without the help of fellow doctoral students in Freiburg: Dr. Matthew Lewis, Dr. Piet Engelke and Dr. Tobias Schubert, who provided the fault simulator and the SAT solvers that I integrated into my ATPG framework Tiguan. In particular, thanks to Matt and Piet, who spent a lot of time optimising their tools and implementing customisations during the initial stage of my doctoral research. Also, thanks to Dr. Stefan Hillebrecht and to Mr. Matthias Sauer for numerous technical discussions.

Thanks also to several people for their cooperation in different works: Prof. Sandip Kundu (University of Massachusetts), Prof. Michel Renovell and Prof. Mariane Comte (Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier), Prof. Dr. Sybille Hellebrand (University of Paderborn), Prof. Dr. Hans-Joachim Wunderlich (University of Stuttgart), Dr. Wolfgang Vermeiren (Fraunhofer Institute for Integrated Circuits, Dresden); and to Mr. Jürgen Schlöffel (Mentor Graphics, formerly NXP Semiconductors GmbH, Hamburg) for providing industrial benchmarks.

Really big thanks to Mr. Peter Winterer, Prof. Becker's system administrator, for taking care of a great deal of computing infrastructure that we students, immersed in the daily grind of doctoral research, sometimes take for granted; and for always being an attentive listener and an obliging colleague.

Finally, my greatest debts. To my former Freiburg colleague, Prof. Dr. Ilia Polian (University of Passau), for his guidance and patience teaching me innumerable skills over a period of ten years; and for proofreading this manuscript at such short notice. *And to my wife Kinga, whom I owe everything else in life.*

Alexander Czutro

### **ABSTRACT**

Modern technologies have enabled the semiconductor industry to enter a new era of integrated-circuit manufacturing. Modern ICs are not only smaller and significantly more high-performing than they used to be only a few years ago; they are also considerably more energy-efficient thanks to the use of new materials with convenient electric properties. However, the use of new materials is also making the fabrication process more difficult to control, and the new chips are more prone to defects. In consequence, the role of fault models that allow to describe complex forms of faulty behaviour is becoming increasingly important in hardware test and diagnosis.

Without doubt, automatic test pattern generation (ATPG) is the most important test task. ATPG algorithms need to be not only run-time-efficient and to produce compact test sets, given the large number of faults that need to be targeted in multibillion-transistor ICs; they also need to keep pace with the development of new mechanisms for the description of faulty behaviour.

Traditionally, ATPG algorithms used in industrial applications are structural, i.e. their reasoning is based on the circuit's structure. However, SAT-based algorithms, i.e. methods that map the ATPG problem to the problem of Boolean satisfiability (SAT), have recently started to gain relevance because they perform better than structural methods on important classes of faults.

This doctoral thesis covers the work on SAT-based test pattern generation performed by the thesis's author between 2008 and 2012. It presents the SAT-based ATPG tool Tiguan and explains in detail all important aspects that were considered in order to make Tiguan a highly efficient test pattern generator capable of calculating provably optimal solutions for complex ATPG problems. The most important contributions of the work presented in this thesis can be summarised as follows:

► The general run-time efficiency of SAT-based ATPG was increased through intelligent mapping of the ATPG problem to SAT, through the optimal utilisa-

tion of multiple computing cores, and through the employment of advanced SAT solving techniques.

- ▶ Dynamic compaction was integrated into SAT-based ATPG. This allowed TIGUAN to test all stuck-at faults in ISCAS and ITC'99 circuits using less test patterns than a commercial, structural tool. Regarding the application to industrial circuits, the compaction efficiency gap between SAT-based and structural ATPG was significantly diminished.

- ▶ Generic fault models were defined which allow to represent complex defect behaviour. In addition, a flexible SAT-based framework for the generation of provably optimal test patterns for complex fault models was implemented. The applicability of the framework was illustrated by several example applications whose replication using structural methods is not trivial.

- ► The performed research and the created software code base opened the path to advanced research in small-delay test, variability and fault tolerance.

Each chapter of the thesis focuses on one key aspect, provides a thorough motivation for the work on that aspect, discusses all relevant algorithmic details, presents and analyses extensive experimental results, and points out important directions for future research. To conclude, the thesis reviews selected works by other authors which have benefited from Tiguan's development.

Finally, after a brief summary of the presented topics, the thesis closes with a discussion of the role that SAT-based ATPG is expected to play in future industrial applications.

### ZUSAMMENFASSUNG

Dank moderner Technologien befindet sich die Halbleiterindustrie in einer neuen Ära der Herstellung von integrierten Schaltungen (*integrated circuits* — IC). Moderne ICs sind nicht nur kleiner und deutlich performanter als vor nur wenigen Jahren; sie sind dank des Einsatzes neuer Werkstoffe mit günstigen elektrischen Eigenschaften auch wesentlich energieeffizienter geworden. Allerdings ist das Herstellungsverfahren durch die Verwendung von neuen Werkstoffen auch schwieriger steuerbar geworden, was zur Folge hat, dass die neuen Chips defektanfälliger sind. Vor diesem Hintergrund ist in der Hardwaretest-Forschung insbesondere die Rolle von Fehlermodellen, mit denen komplexe Formen von Fehlverhalten beschrieben werden können, zunehmend wichtiger geworden.

Ohne Zweifel ist die automatische Testmustererzeugung (*automatic test pattern generation* — ATPG) die wichtigste Testaufgabe. ATPG-Algorithmen müssen nicht nur laufzeiteffizient sein und kompakte Testmengen erzeugen, angesichts der großen Zahl von Fehlern, die in ICs mit mittlerweile mehreren Milliarden Transistoren betrachten werden müssen. Sie müssen auch mit der Entwicklung neuer Verfahren für die Beschreibung von Fehlverhalten Schritt halten.

Traditionell sind die ATPG-Algorithmen, die in industriellen Anwendungen eingesetzt werden, strukturell. Das heißt, ihr Suchverhalten wird von der Schaltungsstruktur diktiert. Allerdings haben vor relativ kurzer Zeit auch SAT-basierte Algorithmen angefangen, an Bedeutung zuzunehmen, da sie bei Anwendung auf bestimmte, wichtige Klassen von Fehlern eine bessere Leistung als strukturelle Methoden erbringen. SAT-basiert bedeutet, dass diese Methoden das ATPG-Problem auf das Problem der Boolschen Erfüllbarkeit (*Boolean satisfiability* — SAT) reduzieren.

Diese Dissertation umfasst die Arbeit, die der Autor im Forschungsbereich der SAT-basierten Testmustererzeugung zwischen 2008 und 2012 geleistet hat. Die Arbeit stellt das SAT-basierte ATPG-Werkzeug TIGUAN vor und erklärt im Detail alle wichtigen Aspekte, die berücksichtigt werden mussten, um aus TIGUAN ein

hocheffizientes Testmustererzeugungswerkzeug zu machen, das in der Lage ist, beweisbar optimale Lösungen für komplexe ATPG-Probleme zu berechnen. Die wichtigsten Beiträge der in dieser Dissertation vorgestellten Arbeit können wie folgt zusammengefasst werden:

- ▶ Die allgemeine Laufzeiteffizienz von SAT-basiertem ATPG wurde durch die geeignete Abbildung des ATPG-Problems auf SAT, durch die optimale Nutzung mehrerer Rechenkerne, und durch den Einsatz von fortgeschrittenen SAT-Techniken verbessert.

- ► Ein Verfahren zur dynamischen Kompaktierung wurde in den SAT-basierten ATPG-Algorithmus integriert. Dies ermöglicht Tiguan, alle Stuck-at-Fehler in Iscas- und Itc'99-Schaltungen mit weniger Testmustern zu testen als ein kommerzielles strukturelles ATPG-Werkzeug. Was die Anwendung auf industrielle Schaltungen betrifft, so wurde die Kluft, die es zwischen SAT-basierten und strukturellen Methoden hinsichtlich der Testmengenkompaktheit gab, deutlich verkleinert.

- ▶ Generische Fehlermodelle wurden definiert, mit deren Hilfe sich komplexes Defektverhalten darstellen lässt. Darüber hinaus ist ein flexibles SAT-basiertes Werkzeug entstanden, mit dem die Erzeugung von beweisbar optimalen Testmustern für komplexe Fehlermodelle möglich ist. Die Anwendbarkeit des Konzeptes wurde anhand von mehreren Beispielanwendungen bewiesen, die sich mit strukturellen Methoden schwer realisieren lassen.

- ▶ Die durchgeführte Forschung und die entstandene Software-Codebasis eröffneten den Weg für weitere Forschung über Verzögerungsfehler, Variabilität und Fehlertoleranz.

Jedes Kapitel der Dissertation konzentriert sich auf einen zentralen Aspekt. Es bietet dabei eine gründliche Motivation für die realisierte Arbeit, erklärt alle relevanten algorithmischen Details, präsentiert und analysiert umfangreiche experimentelle Ergebnisse und erarbeitet Ideen für zukünftige Forschung. Am Ende der Arbeit werden ausgewählte Werke von anderen Autoren kurz vorgestellt, die von der Entwicklung von TIGUAN profitiert haben.

Nach einer kurzen Zusammenfassung der vorgestellten Themen widmet sich die Arbeit schließlich einer Diskussion über die Rolle, die man von der SAT-basierten Testmustererzeugung in zukünftigen industriellen Anwendungen erwarten darf.

### **CONTENTS**

1 Preface

| 2 | Intro | oduction | n to the test of digital circuits                      | 1  |

|---|-------|----------|--------------------------------------------------------|----|

|   | 2.1   | The Bo   | oolean algebra                                         | 1  |

|   | 2.2   | Circuit  | ts                                                     | 1  |

|   |       | 2.2.1    | Modelling levels                                       | 1  |

|   |       | 2.2.2    | Gate-level net lists                                   | 1. |

|   |       | 2.2.3    | Sequential circuits                                    | 1  |

|   | 2.3   | Fault n  | nodels                                                 | 2  |

|   |       | 2.3.1    | Defects, faults and errors                             | 2  |

|   |       | 2.3.2    | The stuck-at fault model                               | 2  |

|   |       | 2.3.3    | Delay fault modelling                                  | 2  |

|   | 2.4   | Test ap  | pplication and fault coverage                          | 2  |

|   |       | 2.4.1    | Definitions                                            | 2  |

|   |       | 2.4.2    | Test application                                       | 2  |

|   |       | 2.4.3    | Two-pattern testing                                    | 2  |

|   | 2.5   | Resistiv | ve fault models                                        | 2  |

|   | 2.6   | Fault si | imulation                                              | 3  |

|   | 2.7   | Test pa  | attern generation                                      | 3. |

|   |       | 2.7.1    | Structural test pattern generation for stuck-at faults | 3  |

|   |       | 2.7.2    | Compaction                                             | 4  |

|   |       |          |                                                        |    |

1

### CONTENTS

| 3 | Intr | duction to the SAT problem and to SAT-based ATPG           | 45 |

|---|------|------------------------------------------------------------|----|

|   | 3.1  | Introduction                                               | 45 |

|   | 3.2  | Formal definition of the SAT problem                       | 47 |

|   | 3.3  | SAT solving algorithms                                     | 49 |

|   |      | 3.3.1 The DPLL-Algorithm                                   | 49 |

|   |      | 3.3.2 Modern SAT solvers                                   | 52 |

|   |      | 3.3.3 Incremental SAT solving                              | 55 |

|   |      | 3.3.4 SAT solving with qualitative preferences             | 55 |

|   | 3.4  | The principle of SAT-based ATPG                            | 57 |

|   | 3.5  | Previous and related work                                  | 60 |

|   |      |                                                            |    |

| 4 | The  | AT-based test pattern generator TIGUAN                     | 63 |

|   | 4.1  | Introduction                                               | 64 |

|   | 4.2  |                                                            | 67 |

|   |      |                                                            | 67 |

|   |      | 4.2.2 Example application to gate-exhaustive testing       | 68 |

|   | 4.3  |                                                            | 69 |

|   | 4.4  | Generation of SAT formulae                                 | 70 |

|   | 4.5  | Post-processing                                            | 75 |

|   | 4.6  | Evaluation of Tiguan's performance                         | 78 |

|   |      | 4.6.1 Stuck-at faults                                      | 78 |

|   |      | 4.6.2 CMS@ faults with non-empty aggressor sets            | 89 |

|   | 4.7  | Conclusions                                                | 94 |

| 5 | Opti | mising the run-time of SAT-based ATPG                      | 95 |

|   | 5.1  | SAT-ATPG with thread-parallel SAT solving                  | 96 |

|   |      | 5.1.1 The SAT solving back-end MiraXT                      | 97 |

|   |      | 5.1.2 Performance of TIGUAN on multi-core architectures 10 | 01 |

|   | 5.2 | SAT-A    | TPG with incremental SAT solving                               | 109 |

|---|-----|----------|----------------------------------------------------------------|-----|

|   |     | 5.2.1    | The SAT solving back-end аntoм                                 | 109 |

|   |     | 5.2.2    | Fault clustering                                               | 111 |

|   |     | 5.2.3    | Experimental evaluation                                        | 115 |

|   | 5.3 | Concl    | usions                                                         | 120 |

| 6 | SAT | -based   | ATPG with dynamic compaction                                   | 123 |

|   | 6.1 | Introd   | uction                                                         | 124 |

|   | 6.2 | The dy   | vnamic compaction procedure                                    | 126 |

|   | 6.3 | Experi   | imental evaluation                                             | 131 |

|   | 6.4 | Enhan    | ced dynamic compaction                                         | 138 |

|   | 6.5 | Conclu   | usions                                                         | 149 |

|   |     |          |                                                                |     |

|   |     |          |                                                                |     |

| 7 | Con | nplex fa | ult models and optimisation problems                           | 153 |

|   | 7.1 | Introd   | uction                                                         | 154 |

|   | 7.2 | CMS@     | 9-based SAT-ATPG for resistive-bridging faults                 | 155 |

|   | 7.3 | The E0   | CMS@ fault model                                               | 162 |

|   | 7.4 | Imple    | mentation of ECMS@-based SAT-ATPG                              | 164 |

|   |     | 7.4.1    | Maximisation and minimisation of $\omega$                      | 165 |

|   |     | 7.4.2    | Forcing $\omega$ to lie between application-specific bounds $$ | 167 |

|   |     | 7.4.3    | Controlling the parity of $\omega$                             | 168 |

|   | 7.5 | Advan    | aced applications of the ECMS@FM                               | 168 |

|   |     | 7.5.1    | Controlling the amount of fault-affected POs                   | 168 |

|   |     | 7.5.2    | SAT-ATPG with control of switching activity                    | 171 |

|   |     |          |                                                                |     |

### **CONTENTS**

| 8  | Powe      | er droop testing                                                         | 179 |

|----|-----------|--------------------------------------------------------------------------|-----|

|    | 8.1       | Introduction                                                             | 180 |

|    | 8.2       | Power droop testing                                                      | 182 |

|    | 8.3       | Mapping to ECMS@-based SAT-ATPG                                          | 185 |

|    | 8.4       | Experimental evaluation                                                  | 188 |

|    |           | 8.4.1 Comparison to structural ATPG                                      | 188 |

|    |           | 8.4.2 Evaluation of strategies for the selection of control lines . $$ . | 190 |

|    | 8.5       | Conclusions                                                              | 194 |

| 9  | Appl      | ications to process variations and fault tolerance                       | 195 |

|    | 9.1       | Introduction                                                             | 196 |

|    | 9.2       | The Tiguan library                                                       | 197 |

|    | 9.3       | Grading of strong fault secureness                                       | 200 |

|    | 9.4       | Optimisation of the KLPG-Algorithm                                       | 203 |

|    | 9.5       | Conclusions                                                              | 207 |

|    |           |                                                                          |     |

|    |           |                                                                          |     |

| 10 | Sum       | mary and concluding remarks                                              | 209 |

|    |           |                                                                          |     |

|    |           |                                                                          |     |

| A  | Beno      | hmark details                                                            | 219 |

|    |           |                                                                          |     |

|    | A 111 t L | nor's publications                                                       | 222 |

|    | Auu       | ioi s publications                                                       | 223 |

|    | Bibli     | ography                                                                  | 227 |

### **LIST OF ALGORITHMS**

| 1 | Simple fault simulation                  | 33  |

|---|------------------------------------------|-----|

| 2 | The D-Algorithm                          | 36  |

| 3 | Sub-routines of the D-Algorithm          | 38  |

| 4 | The DPLL-Algorithm                       | 51  |

| 5 | SAT-based ATPG with dynamic compaction   | 127 |

| 6 | Enhanced dynamic compaction for SAT-ATPG | 139 |

### **LIST OF FIGURES**

| 1  | Truth table of a half-adder                                                                                            | 12  |

|----|------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Gate types                                                                                                             | 15  |

| 3  | Gate-level half-adder                                                                                                  | 17  |

| 4  | Cones of influence                                                                                                     | 17  |

| 5  | A two-input multiplexer                                                                                                | 18  |

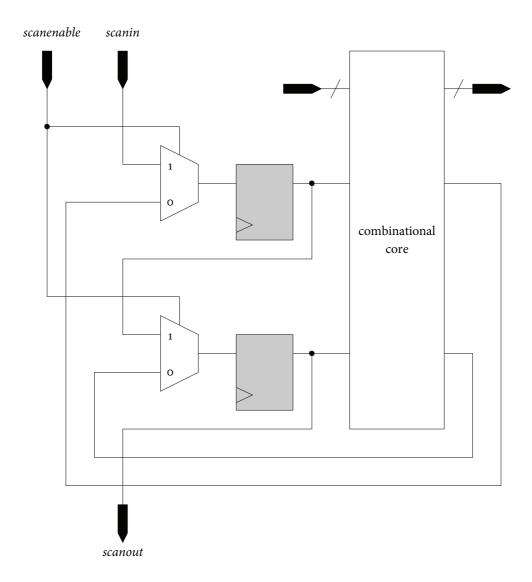

| 6  | Example sequential circuit                                                                                             | 19  |

| 7  | Sequential expansion                                                                                                   | 20  |

| 8  | Test application                                                                                                       | 25  |

| 9  | Scan design                                                                                                            | 28  |

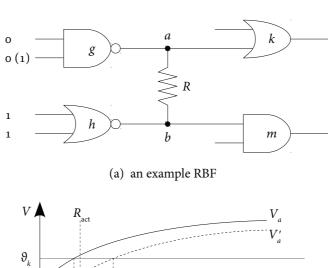

| 10 | Analogue detectability intervals of resistive bridging faults                                                          | 30  |

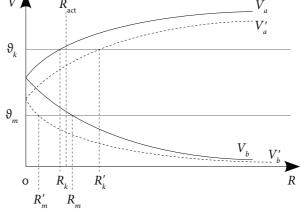

| 11 | D-Algorithm — an example chain of implications                                                                         | 37  |

| 12 | Miter construction and conversion into a SAT formula                                                                   | 58  |

| 13 | Larrabee's miter                                                                                                       | 59  |

| 14 | Tiguan — flow                                                                                                          | 69  |

| 15 | Circuit colouring                                                                                                      | 72  |

| 16 | Assignment of Boolean variables                                                                                        | 73  |

| 17 | Input-output-cone analysis for test relaxation                                                                         | 76  |

| 18 | SAT-ATPG with 32-bit fault dropping for stuck-at faults — average times per run in comparison (columns 7–9 in Table 5) | 83  |

| 19 | MiraXT — design architecture                                                                                           | 100 |

### LIST OF FIGURES

| 20 | Data from Table 15 in graphical form                                                                      | 105 |

|----|-----------------------------------------------------------------------------------------------------------|-----|

| 21 | Generation of the combined SAT instance for a fault cluster                                               | 114 |

| 22 | SAT-ATPG with dynamic compaction — extraction of necessary assignments                                    | 130 |

| 23 | Construction of the fault list                                                                            | 132 |

| 24 | Enhanced dynamic compaction for SAT-ATPG — impact of conflict limit $\alpha$ and fault list sorting       | 142 |

| 25 | Mapping of resistive bridging faults to CMS@ faults                                                       | 156 |

| 26 | Sorting bit arrays using SAT                                                                              | 166 |

| 27 | SAT-ATPG for transition faults with control of switching activity on neighbours — mapping to ECMS@ faults | 173 |

| 28 | Circuit under test connected to power supply                                                              | 182 |

| 29 | Voltage seen by CUT after a $dI/dt$ event                                                                 | 183 |

| 30 | Four-layer power grid                                                                                     | 184 |

| 31 | SAT-ATPG for power droop test — mapping to ECMS@ faults                                                   | 186 |

| 32 | ECMS@-based SAT-ATPG for power droop test — choice of control lines                                       | 193 |

| 33 | Test of a circuit's fault secureness — reduction to ECMS@-ATPG.                                           | 201 |

### **LIST OF TABLES**

| 1  | Gate parameters                                                                                                     | 15  |

|----|---------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Roth's logic [202]                                                                                                  | 36  |

| 3  | The intersection operator                                                                                           | 41  |

| 4  | SAT-ATPG without fault dropping for stuck-at faults — ISCAS and ITC'99 circuits                                     | 79  |

| 5  | SAT-ATPG with 32-bit fault dropping for stuck-at faults — NXP circuits                                              | 80  |

| 6  | SAT-ATPG with 32-bit fault dropping for stuck-at faults — performance comparison with PASSAT [67]                   | 85  |

| 7  | SAT-ATPG without fault dropping for stuck-at faults — classification and performance comparison with PASSAT [86]    | 85  |

| 8  | SAT-ATPG with 32-bit fault dropping for stuck-at faults — comparison with a commercial tool (structural ATPG)       | 87  |

| 9  | SAT-ATPG for stuck-at faults — evaluation of hard-to-detect faults                                                  | 89  |

| 10 | CMS@-based SAT-ATPG with 32-bit fault dropping for gate-exhaustive testing — ISCAS'85, ISCAS'89 and ITC'99 circuits | 90  |

| 11 | CMS@-based SAT-ATPG with 32-bit fault dropping for gate-exhaustive testing — NXP circuits                           | 91  |

| 12 | SAT-ATPG with 32-bit fault dropping for sets of 10,000 random CMS@ faults                                           | 93  |

| 13 | Influence of VSIDS on the SAT solving time                                                                          | 98  |

| 14 | SAT-ATPG with multi-threaded SAT solving for stuck-at faults                                                        | 102 |

|    |                                                                                                                     |     |

| 15 | SAT-ATPG with multi-threaded SAT solving for hard-to-detect stuck-at faults                                                             | 104 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 16 | Two-stage thread-parallel SAT-ATPG for stuck-at faults                                                                                  | 107 |

| 17 | Two-stage thread-parallel CMS@-based SAT-ATPG for gate-exhaustive testing                                                               | 108 |

| 18 | SAT-ATPG with fault clustering for stuck-at faults — without fault dropping                                                             | 116 |

| 19 | SAT-ATPG with fault clustering for stuck-at faults — with 64-bit fault dropping                                                         | 118 |

| 20 | CMS@-based SAT-ATPG with fault clustering for gate-exhaustive testing — with 64-bit fault dropping                                      | 120 |

| 21 | SAT-ATPG for stuck-at faults — static and dynamic compaction — test set size                                                            | 134 |

| 22 | SAT-ATPG for stuck-at faults — static and dynamic compaction — run-time                                                                 | 136 |

| 23 | Enhanced dynamic compaction for SAT-ATPG with topological fault list sorting — impact of conflict limit $\alpha$ — ISCAS circuits       | 144 |

| 24 | Enhanced dynamic compaction for SAT-ATPG with topological fault list sorting — impact of conflict limit $\alpha$ — NXP circuits         | 146 |

| 25 | Dynamic compaction for SAT-ATPG — best Tiguan pattern counts from Tables 23 and 24 in comparison to a commercial tool (structural ATPG) | 148 |

| 26 | CMS@-based SAT-ATPG with 32-bit fault dropping for RBFs — ISCAS'85, ISCAS'89 and ITC'99 circuits                                        | 158 |

| 27 | CMS@-based SAT-ATPG with 32-bit fault dropping for RBFs — NXP circuits                                                                  | 159 |

| 28 | Two-stage thread-parallel CMS@-based SAT-ATPG for resistive-bridging faults                                                             | 161 |

| 29 | ECMS@-based SAT-ATPG for stuck-at faults — controlling the amount of fault-affected primary outputs                                     | 169 |

| 30 | ECMS@-based SAT-ATPG for stuck-at faults — run-time-efficient, nearly-optimal control of the amount of fault-affected primary out-      |     |

|    | puts                                                                                                                                    | 171 |

| 31 | ECMS@-based SAT-ATPG for transition faults — minimising the switching activity of neighbours    | 174 |

|----|-------------------------------------------------------------------------------------------------|-----|

| 32 | ECMS@-based SAT-ATPG for transition faults — controlling the transition direction of neighbours | 175 |

| 33 | ECMS@-based SAT-ATPG for power droop test — comparison to structural ATPG                       | 189 |

| 34 | ECMS@-based SAT-ATPG for power droop test — choice of control lines                             | 191 |

| 35 | Search for longest sensitisable paths with Opt-KLPG (taken from [131])                          | 206 |

| 36 | ISCAS'85 benchmark circuits [32]                                                                | 219 |

| 37 | ISCAS'89 benchmark circuits [31]                                                                | 220 |

| 38 | ITC'99 benchmark circuits [7, 48]                                                               | 221 |

| 39 | Industrial benchmark circuits provided by NXP Hamburg [5]                                       | 222 |

If he had a needle to find in a haystack, he would proceed at once with the diligence of the bee to examine straw after straw until he found the object of his search...

I was a sorry witness of such doings, knowing that a little theory and calculation would have saved him ninety per cent of his labour.

— Nikola Tesla

#### 1

### **PRFFACE**

During the last decade, modern semiconductor technologies have progressed to a level that allows the fabrication of high-performance integrated circuits (IC) that can be deployed into a wide variety of devices of daily use, like mobile phones, "smart watches" and even door locks. In large, this development has been made possible by the increased ability to miniaturise circuit components. In CMOS (Complementary Metal-Oxide-Semiconductor [254]) designs, feature sizes of 45 nanometres and less have become common. But newer technologies have also managed to deal with other important issues. The HKMG (High-k/Metal Gate [105, 35]) technology, for example, is a CMOS variant that replaces silicon dioxide with materials with a higher permittivity, which results in ICs with considerably higher energy efficiency and less heat dissipation. For instance, the heat dissipation of the Exynos 4 processor, a 32nm HKMG chip with four computing cores that can be operated at 1.6 GHz, is so low that the IC is being used in Samsung's newest high-end mobile phones [6]. In comparison, an Intel Pentium 4 (single-core) CPU deployed in desktop PCs in the year 2000 could be operated at a maximum speed of 1.5 GHz and could reach temperatures around 100°C [4].

The downside of these technologies, however, is that the fabrication process is becoming increasingly difficult to control, as the new materials have different properties. In consequence, new chips are more prone to defects. The 2011 International Technology Roadmap for Semiconductors lists the emergence of new technologies as one of the three key driver areas that will shape the future development of test methods and test equipment [10]. Hardware test is one of the most important tasks in the semiconductor production process. And its relevance is not characterised only by the necessity to identify faulty devices. Test and diagnosis are also crucial in that they produce feedback without which the semiconductor industry would not be able to improve their manufacturing processes.

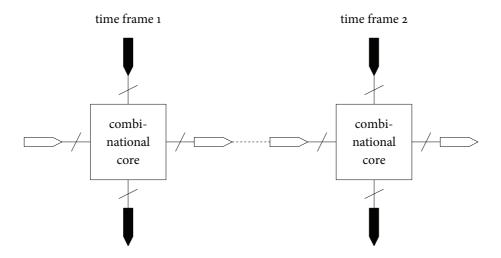

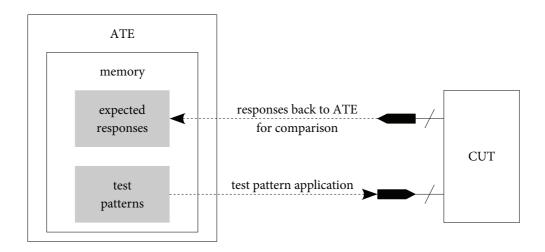

In principle, the *test of a digital circuit* consists of an experiment in which a set of value combinations (*test patterns*) are applied to each manufactured circuit. If the values produced by a *circuit under test* (CUT) differ from the expected responses at any time, then the CUT is known to be defective. In addition, further analysis known as *diagnosis* can be performed on each CUT that fails the test in order to determine the cause of failure.

Expressed in this form, the test experiment may sound simple, but a long path needs to be walked until the test experiment can be performed. The first step is the abstraction of physical reality by means of *formal models*. First, the *digital circuit*, a device that processes input vectors over {0,1} and produces output vectors over the same set, is modelled at a certain level of abstraction. In this thesis, *combinational* circuits are modelled at the *gate level*, and thus regarded as directed acyclic graphs, where the nodes can be either input pins, output pins or logic gates, and the edges are the connections between these components. Each *logic gate* has a specific functionality described by a primitive Boolean function. Thus, the functionality of the whole circuit corresponds to a well-defined Boolean function that maps the circuit's input vectors to the circuit's responses.

Circuits can also have memory elements. Such circuits are called *sequential* and can be modelled as finite-state machines. In many cases, however, it is convenient to ignore the memory elements and to only consider the combinational core. This representation also allows to model the circuit's function over several clock cycles. In this case, several copies of the circuit's combinational core are connected in series, and the *sequential expansion* of the circuit is regarded as one large combinational circuit. In this context, a copy of the circuit at a certain point in time is called a *time frame*.

Also erroneous behaviour needs to be modelled at a certain level of abstraction. This is necessary because the range of possible physical defects is infinite and non-discrete. Therefore, instead of real defects, formal models of defective behaviour are considered during the preparation of the test experiment. Each model of defective behaviour is called a *fault model*. It comprises a set of assumptions that specify the amount of *faults* that need to be considered and the effect that their occurrence induces in a circuit. The most important property of fault models is that they reduce the complexity of the problem. For instance, particle-induced defects cannot be listed exhaustively, as there are infinitely-many possible particle shapes and the exact location of the particle is a continuous parameter [179]. In contrast, fault models define a finite or at least countable number of faults.

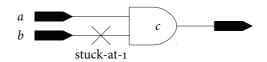

The most-used fault model is the (single) stuck-at fault model [72, 90], which assumes that a circuit's faulty behaviour stems from exactly one line being either

stuck-at o or stuck-at 1, i.e. the line permanently has the logic value o or 1, respectively, independently of the value driving the line. The stuck-at fault model is the dominant fault model used in practical applications because test patterns generated for stuck-at faults usually cover many permanent defects, and because the model has the advantage that it defines a relatively small number of faults. However, it has been shown that the stuck-at fault model does not accurately reflect several defect types encountered in the currently dominant CMOS technology [91, 110, 161, 11]. For example, shorts and opens account for a large portion of physical defects in CMOS ICs [91, 49], but the stuck-at fault model provides only a very rough approximation to the behaviour caused by these defects, especially considering that a substantial fraction of shorts and opens are resistive [200]. As a consequence, sophisticated non-standard fault models have been introduced, especially in order to allow modelling of very complex effects involving multiple lines, like capacitive crosstalk [149, 42, 261, 143], ground bounce [236] or power supply noise [228, 229]. Regarding complex fault models, there are two main approaches. The first consists in modelling specific situations individually. However, this approach usually requires the implementation of dedicated algorithms for each individual model, e.g. [77, 182, 118, 92]. Aside from the cost of implementing different algorithms, also the integration of different methods is complicated because each algorithm may need to model the problem at its own abstraction level. For this reason, also a trend towards generic fault models has emerged [64, 144, 119, 158].

Once the models used to represent the circuit and erroneous behaviour have been fixed, automatic test pattern generation (ATPG) can take place. Due to the large number of test patterns that would need to be applied if all possible input combinations were considered ( $2^n$  for a combinational circuit with n input pins), the dedicated generation of test patterns to cover the set of modelled faults is the most important task in testing.

For a fixed fault model, a test pattern p is said to detect a fault f if the response of the fault-free circuit differs from the response of the circuit with the fault f when p is applied to the circuit's inputs. A fault is called detectable if a test pattern exists that detects it. If no such pattern exists, the fault is called undetectable. ATPG is the process of calculating a test pattern that detects a fault f if f is detectable. An ATPG algorithm is called complete if it is guaranteed to find a test pattern if one exists. If a complete algorithm does not find a pattern that detects a fault f, that proves f's undetectability.

Although the fault detection problem for combinational circuits is NP-complete [128], the average complexity of most ATPG instances found in practice is only  $\mathcal{O}(n^3)$  [256, 189]. However, ATPG still remains one of the most challenging tasks

in testing. In order to overcome the problem's complexity, test pattern generation is usually combined with *fault simulation*. After the generation of a certain number of test patterns, these are simulated in order to determine which not yet targeted faults are also detected by them. Faults detected by simulation can be removed from the target fault list, thus reducing the number of test generation instances to be solved. This technique is known as *fault dropping*. Another positive effect of fault dropping is the reduction of pattern count.

Since the cost of test application depends strongly on the number of test patterns to be applied, *test compaction* techniques are employed to further reduce the number of generated tests without loss of fault coverage. Test compaction can be either *dynamic*, in which case the test search is guided such that each generated test is suitable for the detection of a higher number of faults, or *static*, in which case the size of the generated test set is reduced after the test generation process has been completed.

ATPG algorithms that perform the search based on the circuit's structure are called structural. The first steps in structural testing of logic circuits were made by Eldred in 1959 [72], but it was Roth's work at IBM which resulted in the first systematic and complete ATPG method for stuck-at faults — the *D-Algorithm* [201, 202]. The algorithm uses a five-valued logic known as Roth's logic. This logic comprises the following values: the logic values o and 1, the error values D (assigned to lines that should have the value 1 but have the value 0 due to the presence of the fault) and D' (assigned to lines that should have the value o but have the value 1), and the unspecified value x, which is used to represent lines that have not yet been assigned a value by the algorithm. The algorithm assigns the value D or D' to the fault site depending on whether the target fault is a stuck-at-0 or a stuck-at-1 fault, and computes the values that that assignment implies on other lines. When no further implications can be derived, this branch-and-bound algorithm makes decisions, i.e. it assigns values to yet unspecified lines such that the fault effect is propagated towards a primary output and such that the values that have been assigned to lines driven by yet unspecified values can be justified. If a decision leads to a conflict, the algorithm backtracks, i.e. it corrects wrong decisions and computes the implications of the correction. The algorithm terminates when a fault effect becomes visible at a primary output and all assignments are justified, in which case the fault is detectable, or when the complete search space has been exhausted without finding a solution, in which case the fault is proved to be undetectable.

Two important structural algorithms that can be seen as derivatives of the D-Algorithm are *PODEM* (Path-Oriented Decision Making) [98] and *FAN* (Fanout Oriented Test Generation) [89, 87], which speed up the process by restricting the

locations at which decisions can be made, thus reducing the number of backtracking operations. Some structural algorithms implemented in commercial and proprietary ATPG tools are known to be based on FAN, which is an efficient algorithm able to solve a large number of *easy-to-solve* ATPG instances very fast. Most proposed enhancements of these basic ATPG algorithms [140, 218, 93, 159, 250, 108] are structural as well and rely on learning techniques in order to improve the performance of structural ATPG on *hard-to-solve* ATPG instances.

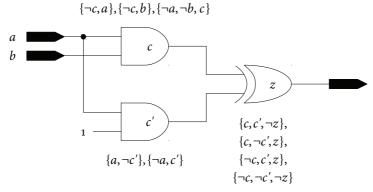

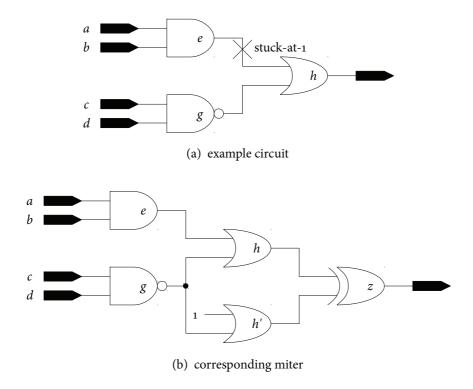

An alternative to structural ATPG algorithms are *SAT-based* methods, i.e. methods that map the ATPG problem to the problem of *Boolean satisfiability*. This is the problem of deciding whether a Boolean formula is *satisfiable*, i.e. whether its variables can be assigned the values o or 1 such that the whole formula evaluates to 1. Software tools used to determine the satisfiability of SAT formulae are called *SAT solvers*. Currently, SAT solvers are used in many fields like planning [136, 96], electronic design automation [166], and verification and test of digital systems [219, 27, 46, 224, 114, 77, 164, 69, 55, 209, 207], especially because many search problems can be converted into SAT problems very efficiently [151].

Given a combinational circuit and a fault f, SAT-based ATPG consists in generating a SAT formula that represents the structure of the circuit both in absence and in presence of the fault. The SAT instance is formulated such that it is satisfiable if and only if f is detectable. If the SAT solver proves that the SAT formula is unsatisfiable, that proves f's undetectability. Conversely, if the SAT solver finds a Boolean assignment that satisfies the SAT formula, f is detectable. Then, the values assigned to the Boolean variables that represent the circuit's primary inputs constitute a test pattern that detects f.

The first approaches to reduce the ATPG problem to a SAT problem were proposed several decades ago [220, 147, 148, 237], but structural algorithms continued to be the standard used in industrial applications due to their better run-times. However, it was shown recently that SAT-based ATPG outperforms structural methods when applied to hard-to-detect and to undetectable faults [242]. The reason for this is that the advances made in SAT solving after the year 2000 were mostly driven by formal-verification problems, i.e. problems in which the equivalence of two models of the same system is to be proved, or in which specific behavioural properties of a system are to be checked. In such problems, the typical workload consists of few, but very hard and usually unsatisfiable SAT instances.

This doctoral thesis covers the contributions to the field of SAT-based test pattern generation made by the thesis's author between 2008 and 2012. Efficient algorithms aimed at enhancing the efficiency of SAT-based ATPG in terms of run-time and test compactness were developed and incorporated into the SAT-based ATPG tool

TIGUAN (Thread-parallel Integrated test pattern Generator Utilising satisfiability ANalysis), which was implemented from scratch paying special attention to the creation of a particularly efficient and extensible code base. In combination with a pattern-parallel fault-simulator [73], TIGUAN is able to classify all stuck-at faults in three suites of well-known academic benchmark circuits. In particular, TIGUAN classifies all stuck-at faults in a suite of industrial circuits without aborts¹, whereas a commercial, structural tool was not able to classify all faults, even using a high conflict limit. In addition, TIGUAN outperforms the SAT-ATPG tool PASSAT developed at the University of Bremen in regard to run-time, number of aborts and test compactness.

A further important contribution is a new dynamic compaction technique specifically designed for the integration into a SAT-ATPG framework, as the rather high pattern count was traditionally considered to be a major drawback of SAT-based methods. Thanks to the new technique, Tiguan is able to generate smaller test sets than a commercial, structural ATPG tool for all academic benchmark circuits.

Like the fault simulator, the two SAT solving engines incorporated into Tiguan were developed within the author's research group, which allowed to implement customisations into the SAT solvers, and to tune their internal parameters so that they could solve the type of SAT instances generated by Tiguan more efficiently. Moreover:

- ▶ The SAT solver *MiraXT* [152, 151] supports thread parallelism. That means that it can distribute the effort of SAT solving among several computation threads that can run in parallel on multi-processor or multi-core systems. The optimal utilisation of this feature was analysed systematically and a *two-stage method* was developed, where faults are processed using different SAT solving parameters depending on the hardness of the produced SAT instances.

- ► The SAT solver ANTOM [217] supports modern, advanced SAT solving techniques:

- Incremental SAT solving with and without assumptions this means that several SAT instances can be solved using only one instantiation of the SAT solver, and that conflict knowledge learnt during the solving of each SAT instance can be shared with subsequent instances, thus

<sup>1</sup>In order to prevent an excessive grow of the total run-time, it is usual for both structural and SAT-based algorithms to *abort* the processing of single faults when a timeout or a conflict limit has been reached. In that case, those faults remain unclassified. A lower number of aborts stands for a higher algorithm quality.

speeding up the solving process. In addition, initial partial assignments (assumptions) can be passed to the SAT solver. Based on this, a *fault clustering* technique was implemented into TIGUAN, which allowed to further reduce the total time needed to classify all stuck-at faults in a suite of nineteen industrial benchmark circuits by 47.7%. For some circuits a reduction of up to 65.3% was achieved.

■ SAT solving with *qualitative preferences* [95, 96, 65] — this is a formal mechanism that allows the user to specify a set of Boolean variables that should be assigned to a preferred value; also the relative importance of those preferences can be laid down. That makes it possible to control with precision the quality of the solutions computed by the SAT solver, and also to formally define solution optimality. This mechanism was employed to implement a SAT-based framework for the generation of test patterns that satisfy user-defined optimisation goals, and the generated test patterns are guaranteed to be optimal. This constitutes a problem class that cannot be solved trivially using structural algorithms.

One of the most important contributions of this thesis is the definition of two generic fault models, the conditional multiple stuck-at fault model (CMS@FM) and the enhanced conditional multiple stuck-at fault model (ECMS@FM), and the incorporation of their support into the SAT-ATPG tool TIGUAN. As was explained previously, the stuck-at fault model no longer suffices to cover all types of defects that occur increasingly in newer technologies. Using the CMS@FM, it is possible to describe defects that induce faulty behaviour on an arbitrary number of victim lines, and to specify the activation conditions for the defect by imposing specific values on a number of aggressor lines. A particular feature of CMS@-based SAT-ATPG is its flexibility, which allows the description of ATPG problems with varying degrees of complexity without the need to modify the SAT-ATPG core engine. For example, CMS@-ATPG was used to generate with equal comfort patterns for relatively simple test concepts, like gate-exhaustive testing [169, 43], and for realistic defect-based models like resistive-bridging faults [198, 199, 197, 75, 78]. In combination with the expansion of sequential circuits, this model can also be used to describe dynamic fault effects.

The ECMS@FM goes even further and supports features not offered by previously existing generic fault models. In combination with SAT solving using qualitative preferences, ECMS@-based SAT-ATPG allows the imposition of *soft constraints* on any number of lines, and thus to control the quality of the generated test patterns with regard to a wide variety of needs. For instance, a set of lines can be chosen and the number of o or 1-assignments made to those lines can be maximised or

minimised. Some of the example applications based on this principle and discussed in detail in this thesis include:

- ▶ The generation of test patterns that maximise the number of primary outputs towards which the fault effect is propagated. Such test patterns have been shown to increase the coverage of transition delay faults [247].

- ► The generation of test patterns that minimise the number of fault-affected primary outputs, which finds application e.g. in diagnosis [124].

- ▶ The generation of test patterns that control precisely the switching activity of a number of selected lines, or globally. For instance, slow-down-crosstalk testing [30] requires that a number of aggressor lines switch in the opposite direction in which the victim line switches, such as to increase the fault effect.

The ECMS@-based SAT-ATPG framework was submitted to a hard test by employing it to generate test sequences for *power droop* testing [245, 177]. Triggered by two different mechanisms over a large number of clock cycles, power droop is a signal integrity issue that leads to localised delay effects. ATPG for power droop constitutes an extremely hard variation of sequential test generation, given that a large number of times frames need to be modelled and that three different optimisation objectives need to be satisfied simultaneously.

Finally, large parts of Tiguan's implementation were optimised and documented such as to provide a C++ library that allowed other researchers to use Tiguan as a SAT-ATPG back-end for various applications.

### **ORGANISATION OF THIS THESIS**

Chapters 2 and 3 provide the reader with an introduction to all basic concepts behind the work covered in the thesis. The contents constitute pre-existing knowledge originated in the work of other authors, and references to the original works have been included where appropriate. Chapter 2 concentrates on the basic principles of testing and, in particular, of test pattern generation. Chapter 3 makes a formal introduction of the SAT problem, and discusses the basic algorithms for the solution of this problem. Special attention is given to techniques used by modern SAT solving tools, as the knowledge of these techniques is fundamental to analyse the experimental results presented in later chapters. Then, this chapter focuses on the application of SAT solving to test pattern generation. It introduces the basic principle and reviews previously existing works on SAT-based ATPG.

Chapters 4–6 introduce the SAT-based test pattern generator TIGUAN and discuss the techniques that were developed in order to increase Tiguan's run-time efficiency and compaction ability. Chapter 4 begins with a summary of Tiguan's development history. After the formal introduction of the CMS@FM, the chapter resumes with an accurate description of Tiguan's main algorithms, which operate internally on the CMS@ model. Chapter 5 focuses on techniques to improve Tiguan's run-time efficiency. The first part of the chapter gives insight into the algorithms used by the SAT engine MiraXT, and discusses the analysis that was performed in order to evaluate Tiguan's performance on multi-core systems. The second part of the chapter introduces the SAT engine ANTOM and explains the most important differences between ANTOM and MiraXT from the point of view of a SAT-ATPG application. Then, a fault clustering technique that utilises ANTOM's incremental SAT solving is presented and evaluated. Finally, Chapter 6 discusses the dynamic compaction method that was developed for dedicated incorporation into Tiguan. The chapter also analyses the impact that fault list pre-sorting and a conflict limit have on the performance of the dynamic compaction algorithm.

Chapters 7 and 8 address the application of SAT-based ATPG to complex fault models. Chapter 7 gives a thorough motivation for the need of complex fault models, discusses applications of the CMS@FM, and introduces the ECMS@FM, which enables the specification of optimisation goals. The implementation of ECMS@based SAT-ATPG is explained in detail, and two important applications of the new ECMS@FM are discussed and evaluated. Chapter 8 discusses the previously mentioned application of ECMS@-ATPG to power droop testing, and focuses on strategies to map the original problem to ECMS@-ATPG such as to achieve the best combination of test quality and run-time efficiency.

To conclude the thesis, Chapter 9 discusses further application possibilities for SAT-based ATPG. A C++ library was developed in order to allow client applications to incorporate Tiguan's functionality in the form of a SAT-ATPG back-end engine. The chapter discusses the principles of the interface design, which attempts to achieve maximum flexibility for the client application and efficient communication between the client application and the SAT-ATPG back-end. Then, short summaries of selected works by other authors are presented. These works employ Tiguan as ATPG engine and have relevance in the research areas of process variations and fault tolerance.

Finally, Chapter 10 closes the thesis with a brief summary of the presented topics and a discussion of the role that SAT-based ATPG is expected to play in industrial applications.

Appendix A provides details on the used benchmark circuits.

#### **OWN PUBLICATIONS**

A complete list of all publications by the author of this thesis is provided on pages 223–226. References in the form of a capital letter followed by a number, both enclosed in brackets (for example, [J2]), refer to this publication list.

Note that parts of the work covered in Chapters 4–9 have been previously published in conference or workshop proceedings, as well as in scientific journals. A footnote on the first page of each of these chapters informs the reader which of the author's publications share contents with that specific chapter.

The author's main works, which served as basis for this doctoral thesis, are the following:

- ► [C16]: This is the seminal work in which the SAT-based test pattern generator TIGUAN, the CMS@ fault model and various applications of this fault model were introduced. These topics are covered in Chapter 4 and in Section 7.2.

- ▶ [J2]: This is the journal version of [C16].

- ▶ [W7]: In this work, the performance of TIGUAN based on the utilisation of thread-parallel SAT solving on multi-core architectures was evaluated. This topic is covered in Section 5.1.

- ► [C13]: This work presented a dynamic compaction method for SAT-based ATPG. This topic is covered in Chapter 6.

- ► [C7]: In this work, newest SAT solving techniques were incorporated into TIGUAN. This allowed the development of a fault clustering technique for the enhancement of TIGUAN's run-time performance (this topic is covered in Section 5.2); and the introduction of ECMS@-based SAT-ATPG for the solution of complex test generation problems with optimisation constraints (this topic is covered in Chapter 7).

- ▶ [C5]: In this work, the capabilities of the new ECMS@-based ATPG framework were explored by means of the application to test generation for power droop testing. This topic is covered in Chapter 8.

- ▶ [C18]: This work (and its journal version [J3]) was originally performed for the author's undergraduate studies (Studienarbeit) and published prior to the author's time as a doctoral student. It provided the necessary background knowledge for the work presented in [C5].

All other publication references (a number enclosed in brackets, e.g. [55]) included in the text refer to the general bibliography list, to be found from page 227 onwards.

## Introduction to the test of digital circuits

This chapter provides a preliminary introduction to the area of research covered in this thesis. It is not intended to be an exhaustive introduction to the test of digital circuits, but rather to provide the reader with the background knowledge required to understand this thesis, and to establish the terminology used to refer to certain concepts for which different authors might use diverse terms. Further information on the topics covered in this chapter can be found in well-known text books, for example in [12, 34, 129].

### 2.1 THE BOOLEAN ALGEBRA

The *Boolean algebra* is an algebra over the set  $\mathbb{B} := \{0, 1\}$ . In this algebra, one unary and two binary operations are defined:

- the *negation*  $\neg$ , where  $\neg o = 1$  and  $\neg 1 = 0$ ,

- the conjunction  $\cdot$ , where  $0 \cdot 0 = 0$ ,  $0 \cdot 1 = 0$ ,  $1 \cdot 0 = 0$  and  $1 \cdot 1 = 1$ ,

- and the *disjunction* +, where 0 + 0 = 0, 0 + 1 = 1, 1 + 0 = 1 and 1 + 1 = 1.

Along with these operations, the Boolean algebra is defined by the following axioms:

- *commutativity* a + b = b + a and  $a \cdot b = b \cdot a$  for all  $a, b \in \mathbb{B}$ ,

- ▶ associativity a + (b + c) = (a + b) + c and  $a \cdot (b \cdot c) = (a \cdot b) \cdot c$  for all  $a, b, c \in \mathbb{B}$ ,

- ▶ and *distributivity*  $a + (b \cdot c) = (a + b) \cdot (a + c)$  and  $a \cdot (b + c) = (a \cdot b) + (a \cdot c)$  for all  $a, b, c \in \mathbb{B}$ .

By combination of the three basic operations, more operations can be defined. The most relevant combination is the *exclusive disjunction*  $\oplus$ , a binary operation defined by  $a \oplus b = (a \cdot \neg b) + (b \cdot \neg a)$  for all  $a, b \in \mathbb{B}$ . Note that commutativity and associativity both hold for the exclusive disjunction. Also,  $o \oplus o = 1 \oplus 1 = 0$  and  $o \oplus 1 = 1$ .

In addition, several important properties of the Boolean algebra can be derived from the main axioms. Some examples follow:

- ▶ absorption  $a \cdot (a + b) = a$  and  $a + (a \cdot b) = a$  for all  $a, b \in \mathbb{B}$ ,

- ▶ complement rule  $a + \neg a = 1$  and  $a \cdot \neg a = 0$  for all  $a \in \mathbb{B}$ ,

- ▶ and *De Morgan's law*  $\neg(a+b) = \neg a \cdot \neg b$  and  $\neg(a \cdot b) = \neg a + \neg b$  for all  $a, b \in \mathbb{B}$ .

#### 2.2 CIRCUITS

#### 2.2.1 MODELLING LEVELS

At any level of abstraction, a *digital circuit* can be seen as a device that processes input data and produces output data, where both the input and output data are represented by vectors over  $\mathbb{B}$ . The circuit's *function* is defined by the lengths of the input and output vectors and by the mapping from the input to the output domain. Hence, the simplest representation of a circuit is the *truth table*. For example, Figure 1 shows the truth table of a half-adder, a circuit that takes two arguments a and b and produces two outputs c and d such that the sequence cd is the binary representation of a + b.

| inputs |   | outputs |   |  |

|--------|---|---------|---|--|

| a      | b | с       | d |  |

| 0      | 0 | 0       | 0 |  |

| 0      | 1 | 0       | 1 |  |

| 1      | 0 | 0       | 1 |  |

| 1      | 1 | 1       | 0 |  |

FIGURE 1. TRUTH TABLE OF A HALF-ADDER

However, truth tables are of little practical use for large circuits and for tasks that depend not only on the circuit's function but also on its implementation. Hence, numerous other ways of modelling a circuit are considered in the literature and in practice. In order to organise the different types of models, different *levels of*

abstraction (also called *modelling levels*) are distinguished, but different authors may define different numbers of modelling levels depending on what they want to illustrate [179]. For instance, Hayes defines in [111] three *design levels*: processor level, register level and gate level.

In [253], where the focus lies on design verification and test, a hierarchy composed of four design levels is given. The design process is viewed as a series of transformations that map design descriptions from higher levels to lower levels. The highest modelling level is the behavioural or architecture level which focuses on the functionality of the modelled circuit or system. Given a design specification, the behaviour of the system is specified using algorithmic notation, for example in the form of a hardware description language. The next lower level is the register-transfer level, which contains more structural information in terms of the implemented logic functions, data and control paths. The implementation of logic functions is modelled in the next lower level, the logical or gate level. In this level, a circuit is composed of a number of *logic gates*, where each logic gate is a component with a specific functionality that is defined by a Boolean function. For instance, an AND gate is a component with two inputs a and b and an output c, where  $c = a \cdot b$ . Gates are connected to each other by signal lines. By traversing the circuit in topological order, it is possible to construct a Boolean function that represents the whole circuit. Finally, the lowest level is the *physical* or *transistor level*. In the same way in which circuits can be modelled by gates and connections between gates, gates are internally modelled by transistors and by connections between different transistors or between transistors and power sources  $(V_{\rm DD})$  or ground. The transistor level can be seen as a refinement of the gate level, and sometimes a mixture of both levels can be used for testing. For instance, faults can be modelled at transistor level in order to reflect defects that are more realistic from a physical point of view, but the rest of the circuit may be modelled at gate level such as to avoid unnecessary overhead, for example during simulation tasks.

Some authors also consider a lower level, the *layout level* [129]. In this level, the circuit description encompasses line widths, inter-line and inter-component distances, as well as device geometries.

Throughout this thesis, gate-level modelling is assumed. The advantage of this level is that it can be regarded as technology-independent. In most process technologies, synthesis tools have readily available libraries containing mappings for the basic logic gates. Hence, it is relatively easy to transform a gate-level description into a (technology-dependent) transistor-level description.

#### 2.2.2 GATE-LEVEL NET LISTS

A *digital combinational* circuit *C* is a device with *n* inputs and *m* outputs, whose behaviour can be uniquely specified by a Boolean function  $\varphi_C : \mathbb{B}^n \to \mathbb{B}^m$ .

At the gate level, a combinational circuit is represented by a *gate-level net list*, a directed acyclic graph (N, L), where N is the set of *nodes* and L is the set of *edges*. The set of nodes is composed of the following sub-sets:

- ▶ *G*, the set of *logic gates*,

- ▶ *F*, the set of *fan-out nodes*,

- ► *I*, the set of *inputs*, and

- ▶ *O*, the set of *outputs*.

The edges represent connections between nodes. They are called *signal lines*, *wires* or *nets*. The number of ingoing and outgoing edges of each node is determined by the node's type. The node sets *I* and *O* represent the inputs and outputs of the circuit, respectively. Hence, the former have no ingoing edges and exactly one outgoing edge, while the latter have exactly one ingoing edge and no outgoing edges.

Logic gates have exactly one output (outgoing edge) and one or more inputs (ingoing edges). In this thesis, the output of a gate together with the set of all its inputs are referred to as that gate's *ports*.

Each logic gate  $g \in G$  implements a Boolean function  $\varphi_g : \mathbb{B}^k \to \mathbb{B}$ , where k is the gate's number of inputs. Which function is implemented by g is specified by g's type. For instance, a two-input AND gate implements the logic conjunction, i.e. for every pair of inputs  $a, b \in \mathbb{B}$ , the output produced by the gate equals  $a \cdot b$ .

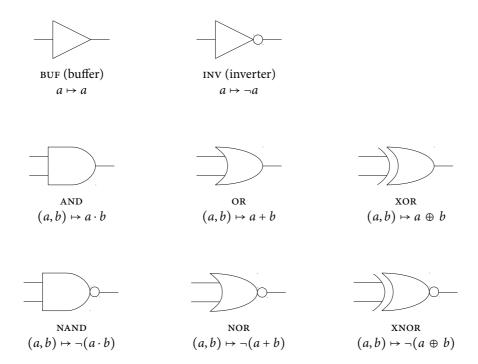

Figure 2 lists all basic gate types considered in this thesis, along with the Boolean function they implement and their symbol in graphical representations of circuits. Although these gates suffice to construct circuits that implement any Boolean function, versions of AND, NAND, OR and NOR gates with more than two inputs are also considered by many authors. However, such gates do not require special attention in the description of algorithms, because their functionality can be expressed in generalised form independently of the number of gate inputs. Thus, the functionality of buffers and inverters can be expressed based on one single parameter called *inversion*. Given an input v, the gate produces the output  $\neg v$  if it is inverting (INV), or the output v if it is not inverting (BUF).

Analogously, the functionality of an AND, NAND, OR or NOR gate g can be described using only two parameters, the gate's *inversion* and the gate's *controlling value* CV(g).

FIGURE 2. GATE TYPES

The Boolean inverse of cv(g) is called g's non-controlling value (ncv(g)). If at least one input of g has the logic value cv(g), then g produces the output value cv(g) independently of the logic value on all other inputs (or the output ncv(g) if g is inverting). g can only produce the output ncv(g) (cv(g) if g is inverting) if all its inputs have the logic value ncv(g). Table 1 lists the inversion, and the controlling and non-controlling values of these four types of gates.

TABLE 1

GATE PARAMETERS

| gate type | inverting | controlling value | non-controlling value |

|-----------|-----------|-------------------|-----------------------|

| AND       | no        | 0                 | 1                     |

| NAND      | yes       | 0                 | 1                     |

| OR        | no        | 1                 | 0                     |

| NOR       | yes       | 1                 | 0                     |

The functionality of XOR and XNOR gates cannot be expressed in this form. Hence, while gate-level-net-list-based algorithms can process all other gate types using a generic procedure that works only in function of the gate's inversion and controlling value, XOR and XNOR gates need to be processed separately.

Since  $a \oplus b = (a \cdot \neg b) + (b \cdot \neg a)$  and  $a \oplus b = \neg(\neg(a \cdot \neg(a \cdot b)) \cdot \neg(b \cdot \neg(a \cdot b)))$  for all  $a, b \in \mathbb{B}$ , xor and xnor gates can also be replaced by equivalent sub-circuits composed of two inverters, two and gates and an or gate, or by equivalent sub-circuits composed of four nand gates, without changing the logic functionality of the circuit. However, this replacement can alter the timing of the circuit and should thus be used only for algorithms that operate only on the logic functionality of the circuit.

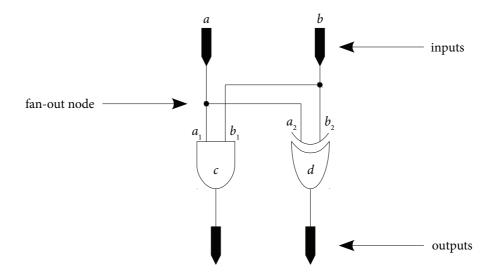

Going back to the definition of the graph (N, L), the set of fan-out nodes F is composed of nodes with one ingoing edge and at least two outgoing edges. The ingoing edge and all outgoing edges of a fan-out node are regarded as one signal that is branched to distribute the output of one gate to multiple other gates. The ingoing edge is called the fan-out's *stem*, while the outgoing edges are called the fan-out's *branches*.

Figure 3 shows an example circuit and illustrates the naming conventions observed in this work. Inputs and gates are denoted by lower case letters. For simplicity, lines are given their own identifiers only when strictly necessary. When that is not the case, they are referred to using the identifier of the gate at which they originate. When necessary, the branches of a fan-out node are denoted by the stem's identifier, but with an index. Circuit outputs are denoted by the identifier of their ingoing edge. The shown circuit represents the functionality of a half-adder (see also Figure 1). Gate c implements the Boolean function  $(a, b) \mapsto a \cdot b$  and gate d implements the Boolean function  $(a, b) \mapsto a \oplus b$ . Hence, the whole circuit implements the Boolean function  $\mathbb{B}^2 \to \mathbb{B}^2$ ,  $(a, b) \mapsto (a \cdot b, a \oplus b)$ .

Let a line connect the output of a gate  $g_1$  to one of the inputs of a gate  $g_2$ . Then,  $g_2$  is called a *successor gate* of  $g_1$ , and  $g_1$  is called a *predecessor gate* of  $g_2$ .

If the output of  $g_1$  is connected to a fan-out node, then all gates connected to the fan-out branches of that node are  $g_1$ 's successors, and  $g_1$  is a predecessor of all those gates.

The sequence of gates  $g_1, \ldots, g_k$  is called a *path* from  $g_1$  to  $g_k$  if  $g_{i+1}$  is a successor gate of  $g_i$  for all  $i = 2, \ldots, k$ . A path is said to be *complete* if it starts at a circuit input and ends at a circuit output. A path that is not complete is called *partial*. For a gate  $g_i$ , the input of  $g_i$  that is connected to  $g_{i-1}$  is called the *on-path* input of  $g_i$ , as that line belongs to the path. All other inputs of  $g_i$  are called *off-path* inputs.

FIGURE 3. GATE-LEVEL HALF-ADDER

FIGURE 4. CONES OF INFLUENCE

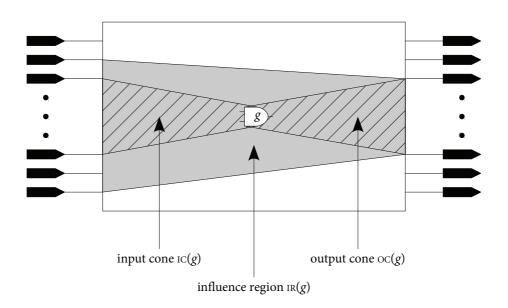

The *output cone* of a gate g (OC(g)) is defined as the set of all gates that belong to a path between g and any circuit output, while the *input cone* of g (IC(g)) is defined as the set of all gates that belong to a path between any circuit input and g. Let  $g_1, \ldots, g_n$  be all circuit outputs contained in OC(g). Then, the set  $IR(g) := IC(g_1) \cup \cdots \cup IC(g_n)$  is called g's *influence region* (Figure 4).

The number of fan-out nodes and the average number of fan-out branches per node are a factor that strongly influences the run-time efficiency of many algorithms that work on gate-level net lists. Hence, some algorithms partition the circuit into fan-out-free regions (FFR), i.e. sub-circuits without fan-out nodes, and then process each FFR separately. Each FFR has the form of a tree, where its root gate is connected either to a circuit output or to a fan-out node. The partition of a circuit into FFRs is unique.

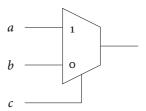

FIGURE 5. A TWO-INPUT MULTIPLEXER

To close this section, Figure 5 shows the symbol used in this thesis to represent *multiplexers*. A two-input multiplexer is a circuit that implements the Boolean function  $(a, b, c) \mapsto (c \cdot a) + (\neg c \cdot b)$ , i.e. the control input c selects which of the two inputs a and b is passed to the output.

### 2.2.3 SEQUENTIAL CIRCUITS

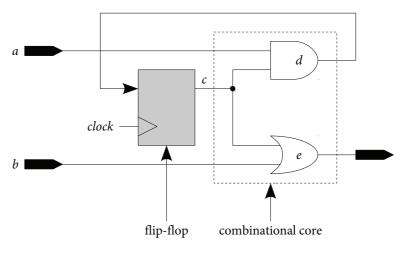

A *digital sequential* circuit is a circuit that contains cycles due to the presence of memory elements, mostly *flip-flops*. Flip-flops are *clocked*, i.e. they are connected to a device that generates a *clock signal*. The clock signal oscillates between logic 1 and logic 0, normally with a 50% duty cycle, and is used to synchronise all flip-flops. These are designed such that they can store a new value only while the clock is high (or only when the clock is low, depending on the implementation). A *clock cycle* is composed of one *falling* (a 1 $\rightarrow$ 0 transition) and one *rising edge* (a 0 $\rightarrow$ 1 transition) of the clock and its length is called *clock period*. This length is denoted by  $T_{clk}$ . In normal operation mode, new input vectors are applied to the sequential circuit once per clock cycle.

(a) sequential circuit

. , 1

FIGURE 6. EXAMPLE SEQUENTIAL CIRCUIT

In contrast to combinational circuits, the functionality of sequential circuits cannot be simply specified by a Boolean function. Instead, a sequential circuit C with n inputs, m outputs and k flip-flops can be regarded as an implementation of a finite-state machine [171] with  $2^k$  or less states. The states are encoded by the data stored in the flip-flops, while the *combinational core* of the circuit computes the output function  $\varphi_C: \mathbb{B}^n \times \mathbb{B}^k \to \mathbb{B}^m$  and the transition function  $\tau_C: \mathbb{B}^n \times \mathbb{B}^k \to \mathbb{B}^k$ , which depend both on the inputs and on the present state. The  $\varphi_C$ -values correspond to the circuit's outputs, while the  $\tau_C$ -values are stored back into the flip-flops.

FIGURE 7. SEQUENTIAL EXPANSION

An example sequential circuit is shown in Figure 6 (a). In this example, n = 2, m = 1 and k = 1. The corresponding state machine has two states, 0 and 1, encoded by c.  $\varphi_C$  maps (a, b, c) to b + c and  $\tau_C$  maps (a, b, c) to  $(a \cdot c)$ .

When fault simulation or test pattern generation are applied to sequential circuits, it is often convenient to ignore the flip-flops and to only consider the combinational core (Figure 6 (b)). The outputs of flip-flops (c in the example) are then treated as additional inputs of the combinational core. These are called *pseudo-primary* or *secondary inputs* (SI). The inputs of memory elements (d in the example) are treated as additional outputs of the combinational core. These are called *pseudo-primary* or *secondary outputs* (SO). Regular inputs and outputs (a, b and e) are then called *primary inputs* (PI) and *primary outputs* (PO), respectively. Instead of the output function  $\varphi_C$  and the transition function  $\tau_C$ , only one global Boolean function is considered:  $\varphi_C^{\text{seq}} : \mathbb{B}^{n+k} \to \mathbb{B}^{m+k}$ , which is computed by the combinational core. In the example,  $\varphi_C^{\text{seq}}$  maps (a, b, c) to  $(b + c, a \cdot c)$ .

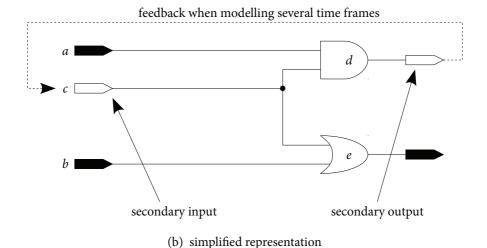

This representation also allows to model the circuit's function over several clock cycles. In this case, several copies of the circuit's simplified representation are connected in series, where the correspondence between secondary outputs and secondary inputs that are connected to the same flip-flop in the original circuit has to be observed (Figure 7). In this context, a copy of the circuit at a certain point in time is called a *time frame*.

### 2.3 FAULT MODELS

### 2.3.1 DEFECTS, FAULTS AND ERRORS

In engineering, models bridge the gap between physical reality and mathematical abstraction. This is especially true in the test of digital circuits since the range of possible physical defects is infinite and non-discrete. For this reason, the modelling of faulty behaviour is one of the most important issues that need to be considered for the development and application of test algorithms.

Bushnell and Agrawal distinguish between three different terms: defects, faults and errors [34]. A *defect* is the unintended difference between the implemented hardware and its intended design. However, in this case, the term only refers to defects that result from the imperfection of the manufacturing process, not to design defects. Some typical defects in VLSI chips are [122]:

- process defects missing or broken contacts, parasitic transistors, shorts, oxide breakdown, etc.,

- ▶ material defects cracks, crystal imperfections, surface impurities, etc.,

- ▶ age defects dielectric breakdown, electromigration, etc.,

- ▶ package defects contact degradation, seal leaks, etc.